由于常规的芯片没有考虑到辐照的影响,无法保证其能在辐照环境下长期稳定工作,因此,我们需要对辐照所带来的影响进行针对性研究及设计,使芯片可以在辐照环境下稳定工作。辐照因素主要包括辐照总剂量、单粒子效应等,这些效应会使集成电路的性能衰减,出现逻辑错误或永久性损坏。一般采取抗辐照加固的方法有设计加固和工艺加固,通过采用合适有效的技术来解决空间辐照对芯片的影响。

1、版图加固设计技术

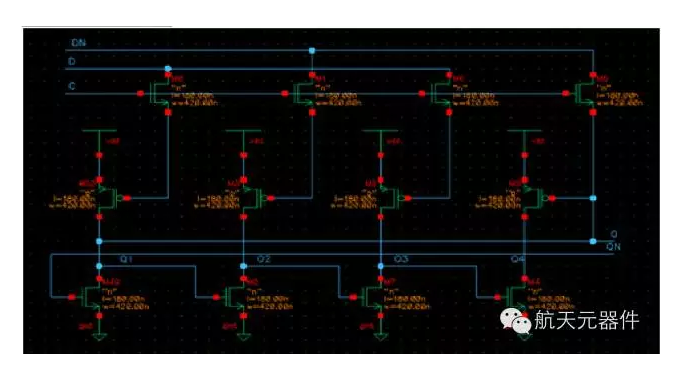

(1)抗单粒子翻转的版图设计方法 避免单粒子翻转主要靠电路设计来实现,但在版图设计中,优化某些细节也可以提高抗单粒子效果。如在下图所示的DICE(Dual interlocked storage cell)单元中,根据仿真结果,在版图设计时,Q4和Q3可以接近,Q1和Q2可以放在一起,因为如果Q3,Q4同时被打翻,输出不变。同理,Q1和Q2也如此,但是Q1和Q4,Q2和Q3之间应保持距离,尽量分开。因为它们同时被打翻时无法返回的临界阈值非常小。

(2)抗单粒子闩锁的版图设计方法 根据单粒子闩锁原理分析,版图设计采用以下方法可以有效提高抗单粒子闩锁能力。 A.采用双保护环结构可以有效减少闭锁效应的发生。在PMOS外围加N+保护环吸收少子,N+保护环接高电位,在NMOS外围作P+保护环吸收少子,P+保护环接GND。P+和N+保护环上尽量以对称位置多打衬底孔。以减小有害的电位梯度。 B.减少阱电阻和衬底电阻,以减小两个寄生管中任何一个的β值,这可以通过增加版图间距来实现。 C.同时还可以通过加粗电源线和地线,加伪收集极来减少闩锁效应。

(3)总剂量效应(TID)

版图设计中做好以下几点,芯片的抗总剂量能力可以得到有效保证。 不同电位的NDIFF或NWELL之间加P+隔离环,P+隔离环接GND。避免场寄生管漏电。 用于做PMOS/NMOS栅极的POLY要分开,用metal走线,并避免在其它地方用POLY走线,特别注意不能跨越不同电位的N型区,避免形成场寄生管。 高压NMOS栅极作环型或H型结构,避免源漏之间寄生MOS漏电。将环型或H型栅极结构的高压NMOS作成PCELL,方便版图设计。 上述研究成果,我们可以应用于各种产品设计中,只需根据采用的工艺改进其设计规则,明确具体尺寸即可。

2、电路级抗辐照加固技术

我们研究了CMOS电路单粒子翻转失效机理,研究表明在敏感电路设计中可以通过采用三采样法检测触发器提高芯片的抗辐照能力。

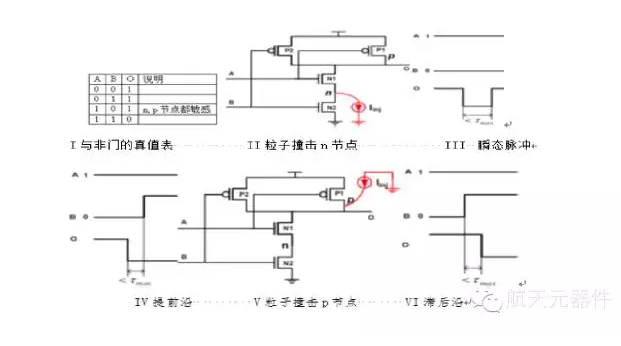

(1)CMOS电路单粒子翻转描述 在CMOS电路中,敏感节点通常是处于关闭状态的晶体管的漏端。粒子撞击所产生的额外电荷将被晶体管的漏端收集,并产生电流尖峰。SEU所产生的脉冲所持续的时间约为100ps。以二输入与非门为例,粒子撞击与非门所产生的影响可描述为,假设输入端A和B的逻辑值分别为‘1’和‘0’,则P1管和N2管处于关闭状态,因此它们的漏端成了敏感节点。图(II)中的电流源用来模拟粒子撞击节点n所产生的效应。图(III)和图(IV)为输出节点的两种不同结果。如果输入端A和B分别保持在逻辑‘1’和‘0’不变,则输出节点出现瞬态脉冲。如果输入端B在粒子撞击时发生变化,输出节点的变化沿将提前。如果其传输路径的延时小于脉冲所持续时间,则提前沿的出现将导致其后的存储单元出现软失效。图(V)和(VI)给出了粒子撞击节点p的情况。这种情况下,如果输入端B在粒子撞击时发生变化,则节点p多余的电荷将增加与非门的延时。如果该延时发生在关键路径上,则可能在电路中产生软失效。滞后沿也称为瞬态延时。另一方面,粒子撞击引起的瞬态脉冲在电路中传输时可能发生改变,它可能被屏蔽,衰减或者继续传输并转变成提前沿、滞后沿或动态错误。

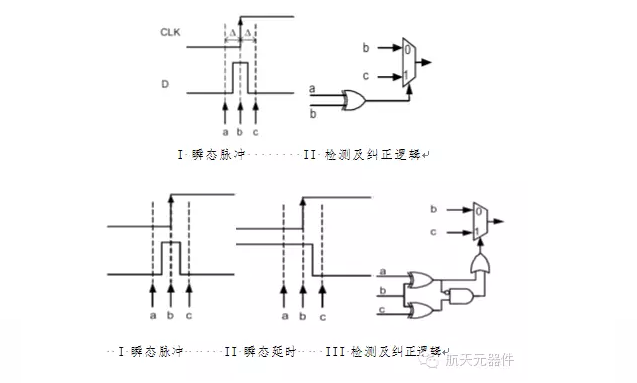

(2)三采样法检测触发器设计 三采样法检测触发器输入端错误脉冲所采用的常规方法。如图所示为采用三采样法检测瞬态脉冲的示意图。CLK和D分别为触发器的时钟和数据输入端。三个采样点分别为a、b和c,该法用来检测并纠正数据输入端可能出现的瞬态脉冲。为保证正确性,两个相邻采样点的间距应该大于瞬态脉冲的最大宽度。

|